ابتكارات جديدة في معالجات IBM لتسريع الذكاء الاصطناعي على أنظمة IBM Z Mainframe من الجيل التالي

معالج IBM Telum II الجديد وIBM Spyre Accelerator يفتحان المجال أمام إمكانات الذكاء الاصطناعي على مستوى المؤسسات، بما في ذلك نماذج اللغة الكبيرة والذكاء الاصطناعي التوليدي

تتيح تقنية الإدخال/الإخراج المتقدمة وتبسط نظام الإدخال/الإخراج الفرعي القابل للتطوير والمصمم لتقليل استهلاك الطاقة وبصمة مركز البيانات

بالو ألتو، كاليفورنيا ، 26 أغسطس 2024 / بي آر نيوزواير/ -- كشفت شركة آي بي إم (المدرجة في بورصة نيويورك تحت الرمز: IBM ) عن تفاصيل البنية التحتية لمعالج IBM Telum® II القادم وجهاز تسريع IBM Spyre™ في مؤتمر Hot Chips 2024. تم تصميم التقنيات الجديدة لتوسيع سعة المعالجة بشكل كبير عبر أنظمة الحواسيب المركزية IBM Z من الجيل التالي، مما يساعد على تسريع استخدام نماذج الذكاء الاصطناعي التقليدية ونماذج الذكاء الاصطناعي ذات اللغات الكبيرة جنبًا إلى جنب من خلال طريقة تجميعية جديدة للذكاء الاصطناعي.

مع انتقال العديد من مشاريع الذكاء الاصطناعي التوليدي التي تستفيد من نماذج اللغة الكبيرة (LLMs) من إثبات المفهوم إلى الإنتاج، برزت المطالبات بالحلول الموفرة للطاقة والآمنة والقابلة للتطوير كأولويات رئيسية. تتوقع أبحاث مورجان ستانلي المنشورة في أغسطس أن متطلبات الذكاء الاصطناعي التوليدي للطاقة سترتفع بنسبة 75٪ سنويًا على مدى السنوات العديدة القادمة، مما يضعها على المسار الصحيح لاستهلاك نفس القدر من الطاقة في عام 2026 كما فعلت إسبانيا في عام 2022.1 يشير العديد من عملاء IBM إلى أن القرارات المعمارية لدعم نماذج الأساس ذات الحجم المناسب ونهج التصميم الهجين لأحمال عمل الذكاء الاصطناعي أصبحت مهمة بشكل متزايد.

وتتضمن الابتكارات الرئيسية التي تم الكشف عنها اليوم ما يلي:

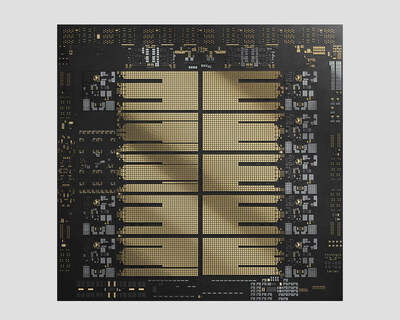

- معالج IBM Telum II: صُمم هذا المعالج لتشغيل أنظمة IBM Z من الجيل التالي، ويتميز بتردد متزايد وسعة ذاكرة ونمو بنسبة 40% في ذاكرة التخزين المؤقت ونواة تسريع الذكاء الاصطناعي المتكاملة بالإضافة إلى وحدة معالجة البيانات (DPU) المتصلة بشكل متماسك مقارنة بشريحة Telum من الجيل الأول. ومن المتوقع أن يدعم المعالج الجديد حلول الحوسبة المؤسسية لـ LLMs، ويخدم احتياجات المعاملات المعقدة في الصناعة.

- وحدة تسريع الإدخال والإخراج: تم تصميم وحدة معالجة البيانات (DPU) الجديدة تمامًا على شريحة معالج Telum II لتسريع بروتوكولات الإدخال والإخراج المعقدة للشبكات والتخزين على الحاسب الآلي الرئيسي. تعمل وحدة معالجة البيانات (DPU) على تبسيط عمليات النظام ويمكنها تحسين أداء المكونات الرئيسية.

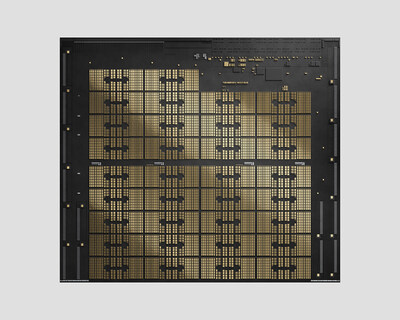

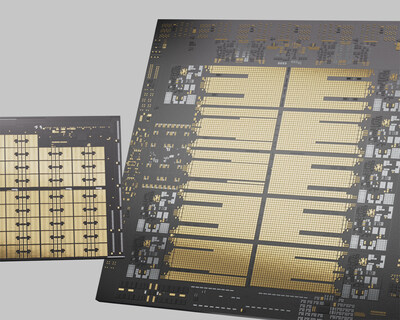

- IBM Spyre Accelerator: يوفر قدرة حوسبة إضافية للذكاء الاصطناعي لتكملة معالج Telum II. من خلال العمل معًا، تشكل شرائح Telum II وSpyre بنية قابلة للتطوير لدعم أساليب التجميع لنمذجة الذكاء الاصطناعي - ممارسة الجمع بين نماذج التعلم الآلي المتعددة أو نماذج الذكاء الاصطناعي للتعلم العميق مع برامج ترميز LLMs. من خلال الاستفادة من نقاط القوة في كل بنية نموذجية، قد يوفر الذكاء الاصطناعي المجمع نتائج أكثر دقة ومتانة مقارنة بالنماذج الفردية. سيتم تسليم شريحة IBM Spyre Accelerator، التي تم عرضها في مؤتمر Hot Chips 2024، كخيار إضافي. يتم توصيل كل شريحة تسريع عبر محول PCIe بقوة 75 وات وتستند إلى تقنية تم تطويرها بالتعاون مع IBM Research. كما هو الحال مع بطاقات PCIe الأخرى، فإن Spyre Accelerator قابلة للتطوير لتناسب احتياجات العميل.

قالت تينا تاركوينيو ، نائب الرئيس لإدارة المنتجات في IBM Z وLinuxONE: "إن خارطة الطريق القوية متعددة الأجيال لدينا تضعنا في وضع يسمح لنا بالبقاء في صدارة اتجاهات التكنولوجيا، بما في ذلك المطالب المتزايدة للذكاء الاصطناعي. تم تصميم معالج Telum II وSpyre Accelerator لتقديم حلول حوسبة مؤسسية عالية الأداء وآمنة وأكثر كفاءة في استهلاك الطاقة. بعد سنوات من التطوير، سيتم تقديم هذه الابتكارات في منصة IBM Z من الجيل التالي حتى يتمكن العملاء من الاستفادة من LLMs والذكاء الاصطناعي التوليدي على نطاق واسع".

سيتم تصنيع معالج Telum II وجهاز IBM Spyre Accelerator بواسطة شريك التصنيع القديم لشركة IBM، Samsung Foundry، وسيتم بناؤهما على عقدة عملية 5nm عالية الأداء وكفاءة الطاقة. من خلال العمل معًا، سيدعمان مجموعة من حالات الاستخدام المتقدمة التي تعتمد على الذكاء الاصطناعي والمصممة لإطلاق العنان لقيمة الأعمال وخلق مزايا تنافسية جديدة. باستخدام أساليب الذكاء الاصطناعي المجمعة، يمكن للعملاء تحقيق نتائج أسرع وأكثر دقة لتوقعاتهم. ستوفر قوة المعالجة المجمعة التي تم الإعلان عنها اليوم منحدرًا لتطبيق حالات استخدام الذكاء الاصطناعي التوليدي. يمكن أن تشمل بعض الأمثلة:

- اكتشاف الاحتيال في مطالبات التأمين: تعزيز اكتشاف الاحتيال في مطالبات التأمين على المنازل من خلال الذكاء الاصطناعي المجمع، والذي يجمع بين LLMs والشبكات العصبية التقليدية المصممة لتحسين الأداء والدقة.

- مكافحة غسيل الأموال المتقدمة: الكشف المتقدم عن الأنشطة المالية المشبوهة، ودعم الامتثال للمتطلبات التنظيمية والتخفيف من مخاطر الجرائم المالية.

- مساعدو الذكاء الاصطناعي: قيادة تسريع دورة حياة التطبيق، ونقل المعرفة والخبرة، وشرح التعليمات البرمجية بالإضافة إلى التحول، والمزيد.

المواصفات ومقاييس الأداء :

معالج Telum II : يتميز بثمانية أنوية عالية الأداء تعمل بتردد 5.5 جيجاهرتز، مع ذاكرة تخزين مؤقتة من المستوى الثاني بحجم 36 ميجابايت لكل نواة وزيادة بنسبة 40% في سعة ذاكرة التخزين المؤقت على الشريحة بإجمالي 360 ميجابايت. توفر ذاكرة التخزين المؤقت الافتراضية من المستوى الرابع بحجم 2.88 جيجابايت لكل درج معالج زيادة بنسبة 40% عن الجيل السابق. يسمح مسرع الذكاء الاصطناعي المتكامل باستنتاج الذكاء الاصطناعي أثناء المعاملات بزمن انتقال منخفض وعالي الإنتاجية، على سبيل المثال تعزيز اكتشاف الاحتيال أثناء المعاملات المالية، ويوفر زيادة بمقدار أربعة أضعاف في سعة الحوسبة لكل شريحة عن الجيل السابق.

تم دمج وحدة تسريع الإدخال/الإخراج DPU الجديدة في شريحة Telum II. وهي مصممة لتحسين معالجة البيانات من خلال زيادة كثافة الإدخال/الإخراج بنسبة 50%. يعمل هذا التقدم على تعزيز الكفاءة الشاملة وقابلية التوسع في IBM Z، مما يجعله مناسبًا تمامًا للتعامل مع أحمال عمل الذكاء الاصطناعي واسعة النطاق والتطبيقات كثيفة البيانات في الشركات اليوم.

Spyre Accelerator : مسرع مصمم خصيصًا للمؤسسات يوفر إمكانيات قابلة للتطوير لنماذج الذكاء الاصطناعي المعقدة وحالات استخدام الذكاء الاصطناعي التوليدية. يتميز بسعة ذاكرة تصل إلى 1 تيرابايت، تم تصميمها للعمل جنبًا إلى جنب عبر البطاقات الثمانية لدرج الإدخال والإخراج العادي، لدعم أحمال عمل نماذج الذكاء الاصطناعي عبر الإطار الرئيسي مع تصميمها بحيث لا تستهلك أكثر من 75 وات لكل بطاقة. ستحتوي كل شريحة على 32 نواة حوسبة تدعم أنواع البيانات int4 وint8 وfp8 وfp16 لكل من تطبيقات الذكاء الاصطناعي منخفضة زمن الوصول وعالية الإنتاجية.

التوفر

سيكون معالج Telum II هو المعالج المركزي الذي سيعمل على تشغيل الجيل التالي من منصات IBM Z وIBM LinuxONE. ومن المتوقع أن يتوفر لعملاء IBM Z وLinuxONE في عام 2025. ومن المتوقع أيضًا أن يتوفر IBM Spyre Accelerator، الذي لا يزال في مرحلة المعاينة التقنية، في عام 2025.

إن البيانات المتعلقة بالتوجهات المستقبلية لشركة IBM ونواياها تخضع للتغيير أو السحب دون إشعار، وتمثل الأهداف والغايات فقط.

نبذة عن شركة IBM

تعد شركة IBM من الشركات الرائدة عالميًا في توفير خدمات الحوسبة السحابية الهجينة والذكاء الاصطناعي والاستشارات. نحن نساعد العملاء في أكثر من 175 دولة على الاستفادة من البيانات وتبسيط العمليات التجارية وخفض التكاليف واكتساب الميزة التنافسية في صناعاتهم. تعتمد آلاف الجهات الحكومية والشركات في مجالات البنية التحتية الحيوية مثل الخدمات المالية والاتصالات والرعاية الصحية على منصة الحوسبة السحابية الهجينة من IBM وRed Hat OpenShift للتأثير على التحولات الرقمية الخاصة بهم بسرعة وكفاءة وأمان. توفر ابتكارات IBM الرائدة في مجال الذكاء الاصطناعي والحوسبة الكمومية وحلول الحوسبة السحابية الخاصة بالصناعة والاستشارات خيارات مفتوحة ومرنة لعملائنا. كل هذا مدعوم بالتزام IBM الطويل الأمد بالثقة والشفافية والمسؤولية والشمول والخدمة.

مصادر إضافية

- اقرأ المزيد عن معالج IBM Telum II.

- اقرأ المزيد عن IBM Spyre Accelerator.

- اقرأ المزيد عن IO Accelerator

جهة الاتصال الإعلامية:

تشيس سكينر

اتصالات آي بي إم

مطاردة.سكينر@ibm.com

ايشواريا بول

اتصالات آي بي إم

عيش.بول@ibm.com

1 المصدر: مورجان ستانلي للأبحاث، أغسطس 2024 .

![]() يمكنكم الاطلاع على المحتوى الأصلي لتنزيل الوسائط المتعددة على الرابط التالي: https://www.prnewswire.com/news-releases/new-ibm-processor-innovations-to-accelerate-ai-on-next-generation-ibm-z-mainframe-systems-302229993.html

يمكنكم الاطلاع على المحتوى الأصلي لتنزيل الوسائط المتعددة على الرابط التالي: https://www.prnewswire.com/news-releases/new-ibm-processor-innovations-to-accelerate-ai-on-next-generation-ibm-z-mainframe-systems-302229993.html

المصدر IBM